Matching the width of a BRAM, for instance, can go a long way to allowing the design to run at the highest speed. Other coding considerations involve ensuring that the size of your shift register is appropriate for the targeted block RAM (BRAM) in the FPGA. In many FPGAs, a more compact design is synthesized when the reset only needs to be applied to one register element. Since some architectures only support a single reset line for a group of flip- flops, forcing each register to reset may cause only one flip- flop in a group to be utilized, stretching the design across several configurable logic blocks (CLBs). Using a reset on the entire register bank will potentially cause an increase in resource utilization in the FPGA. One of the most important is how you reset the shift register–applying a reset to all the registers (as shown in the example) or only the first register. #VHDL PROGRAM FOR LEFT SHIFT REGISTER CODE#The code example implements both a single- and multi- bit shift register. #VHDL PROGRAM FOR LEFT SHIFT REGISTER GENERATOR#PN sequence generator using linear feedback shift register in VHDL. #VHDL PROGRAM FOR LEFT SHIFT REGISTER SERIAL#N bit shift register (Serial in Serial out). Subscribe Subscribed Unsubscribe 23,622 23K. Shift Registers in VHDL Columbia Gorge Community College. I can make a right shift using example code as follows and it works. I have created code for 8 bit shift register left. With suitable gating arrangement a serial shift register can perform both operations. 4 bit shift left, shift register problem. Pls send me verilog code for 4-bit shift register using behavioral modelling. This is because Verilog does not allow bulk addressing of memory types, which is how Verilog classifies two dimensional arrays. If you want to shift multiple bits at a time (e. A single- bit shift register can be implemented in Verilog using concatenation.

Depending on the implementation method (code or IP), any practical dimensions can be used. The above illustration shows a single- bit wide shift register with a length of 8, but there is nothing special about those numbers.

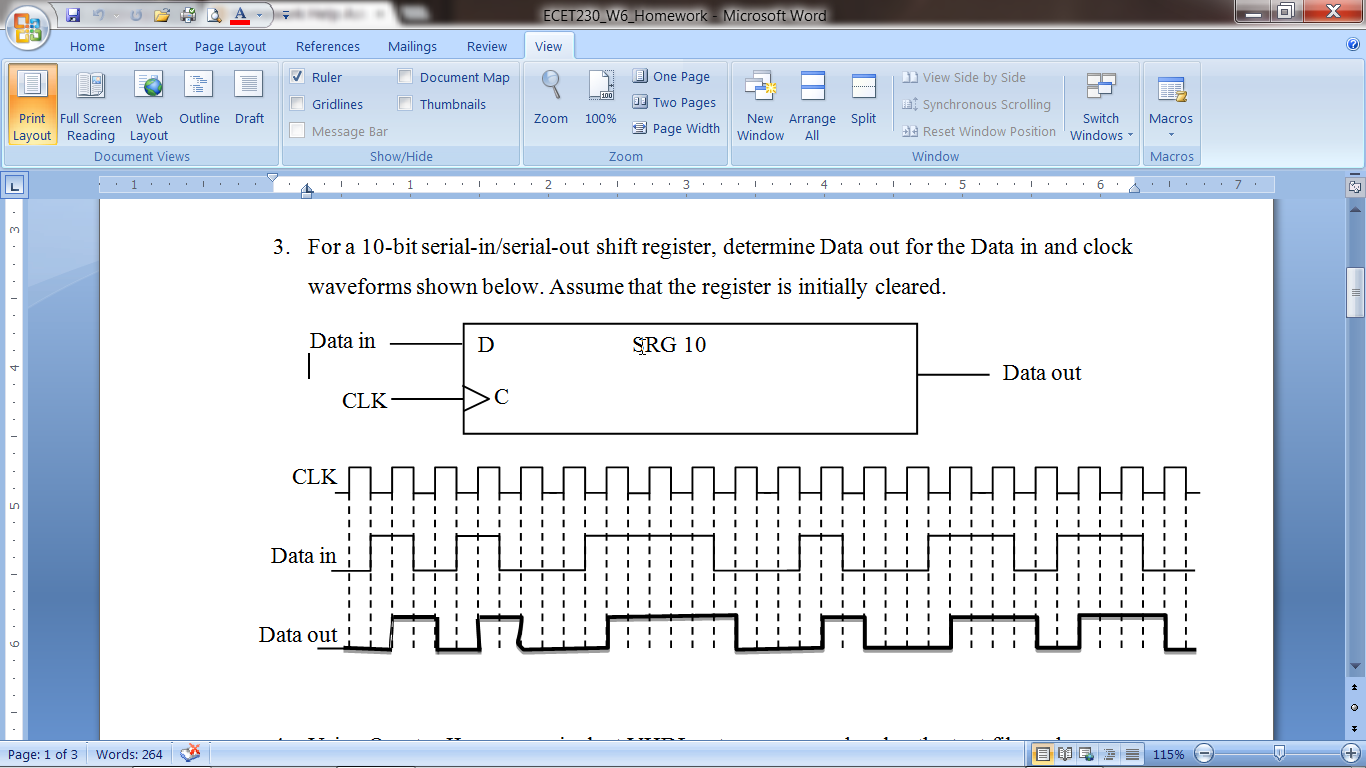

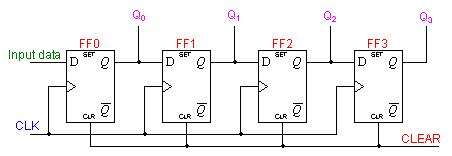

An illustration of a shift register is shown below, where data is entering the register chain at the least significant bit (LSB), or the right side of the picture. In some designs, every register element can be accessed individually, while other implementations only allow access at specific locations. Cz temp's value is retained already by the flip-flop.Verilog Shift Register. I.e., the temp's value is assigned to Q only in the next clock edge. THIS VALUE of temp is captured ONLY in the next edge by the flip-flop for Q. If temp is updated in one clock edge with the value of D. When you write this piece of code, it will infer two flip-flops connected back to back. In VHDL, this is called signal scheduling. "Theoretically something like this should show the outputs q to be the same as input d" However I have some suggestions in your code.ġ) Process needs only clk and rst in the sensitive list, as the rest are synchronous signals as per your code. There are known issues between these two constructs in some simulators. Check rising_edge(clk) instead of clk=1 clk'event.

#VHDL PROGRAM FOR LEFT SHIFT REGISTER SIMULATOR#Your simulator is never entering into your clock block. So it seems like it is a simulator issue here or mistake in the way you simulated this design. It gave the expected waveforms as per your code. I checked this in modelsim 6.5, 10.4 and iSim 14.7. I cannot find a fix for this or infact all the modes (s= 00, 01, 10, 11) show no changes in the output. Theoretically something like this should show the outputs q to be the same as input d Therefore the signal temp is assigned with input d and then the output q is assigned the signal temp. I tried running this on Xilinx ISE simulator but when I simulate the waveform, there seems to be no changes to the outputs.Īs the image above shows, when s = "11", the outputs q should be the same as the inputs d as when "11" => Signal temp: std_logic_vector(3 downto 0) I have managed to write the code which from reviewing it a couple of times, seems without errors (I understand sometimes the code can compile successfully but in fact there would be a few problems in there which aren't so obvious). #VHDL PROGRAM FOR LEFT SHIFT REGISTER SOFTWARE#I am also using Xilinx software to simulate the VHDL code. I am designing a universal shift register of 4 bits in VHDL.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed